3.2. INTRODUCCIÓN AL VHDL

En los inicios de la década de 1980, los rápidos avances en la tecnología de los circuitos integrados impulsaron el desarrollo de prácticas estándar de diseño para los circuitos digitales. VHDL se creó como parte de tal esfuerzo y se convirtió en el lenguaje estándar industrial para describir circuitos digitales, principalmente porque es un estándar oficial de la IEEE. En 1987 se adoptó la norma original para VHDL, llamada IEEE 1076. En 1993 se adoptó una norma revisada, la IEEE 1164.

En sus orígenes, VHDL tenía dos propósitos centrales. Primero, servía como lenguaje de documentación para describir la estructura de circuitos digitales complejos. Como estándar oficial del IEEE, ofreció una forma común de documentar los circuitos diseñados por varias personas. Segundo, VHDL aportó funciones para modelar el comportamiento de un circuito digital, lo que permitió emplearlo como entrada para programas que entonces se usaban para simular la operación del circuito. En años recientes, aparte de usarlo para documentación y simulación, VHDL también se volvió popular para el ingreso de diseño en sistemas CAD (diseño asistido por computadora). Las herramientas CAD se utilizan para sintetizar el código de VHDL en una implementación de hardware del circuito descrito.

La estructura general de un programa en VHDL está formada por módulos o unidades de diseño, cada uno de ellos compuesto por un conjunto de declaraciones e instrucciones que definen, describen, estructuran, analizan y evalúan el comportamiento de un sistema digital.

Existen cinco tipos de unidades de diseño en VHDL: declaración de entidad (entity declaration), arquitectura (architecture), configuración (configuration), declaración del paquete (package declaration) y cuerpo del paquete (package body). En el desarrollo de programas en VHDL pueden utilizarse o no tres de los cinco módulos, pero dos de ellos (entidad y arquitectura) son indispensables en la estructuración de un programa.

3.2.1. ENTIDAD (ENTITY)

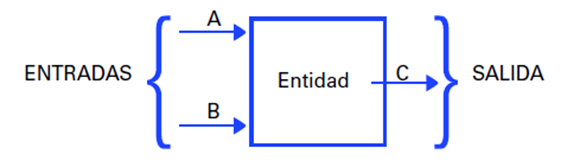

Una entidad (entity) es el bloque elemental de diseño en VHDL, Las entidades son todos los elementos electrónicos (sumadores, contadores, compuertas, flip-flops, memorias, multiplexores, etc.) que forman de manera individual o en conjunto un sistema digital. Una entidad, entonces, puede verse como la estructura del hardware, que describe sus entradas y salidas.

Cada una de las señales de entrada y salida en una entidad son referidas como puerto, el cual es similar a una terminal (pin) de un símbolo esquemático. Todos los puertos que son declarados deben tener un nombre, un modo y un tipo de dato.

NOMBRE. Se utiliza como una forma de llamar al puerto.

MODO. Permite definir la dirección en la cual el dato es transferido a través de un puerto. Un modo puede tener uno de cuatro valores:

- IN (entrada): Se refiere a las señales de entrada a la entidad. Este sólo es unidireccional y nada más permite el flujo de datos hacia dentro de la entidad.

- OUT (salida): Indica las señales de salida de la entidad.

- INOUT (entrada/salida): Permite declarar a un puerto de forma bidireccional, es decir, de entrada/salid; además permite la retroalimentación de señales dentro o fuera de la entidad.

- BUFFER: Permite hacer retroalimentaciones internas dentro de la entidad, pero a diferencia del modo inout, el puerto declarado se comporta como una terminal de salida.

TIPOS DE DATOS. Los tipos son los valores (datos) que el diseñador establece para los puertos de entrada y salida dentro de una entidad; se asignan de acuerdo con las características de un diseño en particular. Algunos de los tipos más utilizados en VHDL son:

• Bit, el cual tiene valores de 0 y 1 lógico.

• Boolean (booleano) que define valores de verdadero o falso en una expresión.

• Bit_vector (vectores de bits) que representa un conjunto de bits para cada variable de entrada o salida.

• Integer (entero) que representa un número entero.

Los anteriores son sólo algunos de los tipos que maneja VHDL, pero no son los únicos.

La declaración de una entidad consiste en la descripción de las entradas y salidas de un circuito de diseño identificado como entity (entidad); es decir, la declaración señala las terminales o pines de entrada y salida con que cuenta la entidad de diseño.

Por ejemplo, la forma de declarar la entidad correspondiente al circuito sumador de la siguiente figura se muestra a continuación:

En la línea 1 se inicia la declaración de la entidad con la palabra reservada entity, seguida del identificador o nombre de la entidad (sumador) y la palabra reservada is. Los puertos de entrada y salida (port) se declaran en las líneas 2 y 3, respectivamente, en este caso los puertos de entrada son A, B y Cin, mientras que SUMA y Cout representan los puertos de salida. El tipo de dato que cada puerto maneja es del tipo bit, lo cual indica que sólo pueden manejarse valores de ‘0’ y ‘1’ lógicos. Por último, en la línea 4 termina la declaración de entidad con la palabra reservada end, seguida del nombre de la entidad (sumador).

Debemos notar que, como cualquier lenguaje de programación, VHDL sigue una sintaxis y una semántica dentro del código, mismas que hay que respetar. En esta entidad conviene hacer notar el uso de punto y coma (;) al finalizar una declaración y de dos puntos (:) al asignar nombres a las entradas y salidas.

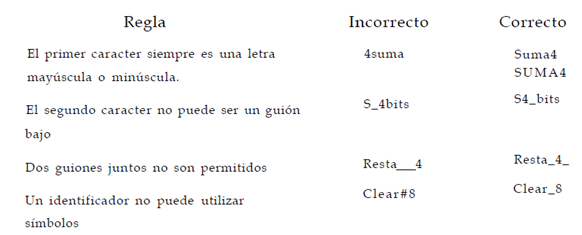

Los identificadores son simplemente los nombres o etiquetas que se usan para referir variables, constantes, señales, procesos, etc. Pueden ser números, letras del alfabeto y guiones bajos ( _ ) que separen caracteres y no tienen una restricción en cuanto a su longitud. Todos los identificadores deben seguir ciertas especificaciones o reglas para que se puedan compilar sin errores, mismas que aparecen en la siguiente tabla:

3.2.2. ARQUITECTURAS (ARCHITECTURE)

Una arquitectura (architecture) se define como la estructura que describe el funcionamiento de una entidad, de tal forma que permita el desarrollo de los procedimientos que se llevarán a cabo con el fin de que la entidad cumpla las condiciones de funcionamiento deseadas. De manera general, los estilos de programación utilizados en el diseño de arquitecturas se clasifican como:

• Estilo funcional

• Estilo por flujo de datos

• Estilo estructural

El nombre asignado a estos estilos no es importante, ya que es tarea del diseñador escribir el comportamiento de un circuito utilizando uno u otro estilo que a su juicio le sea el más acertado. En la siguiente figura se presenta un ejemplo de la descripción de la arquitectura por medio de funciones booleanas.

En el siguiente video se muestra una breve descripción del diseño digital por medio de VHDL:

ACTIVIDAD: Hacer la descripción de Hardware del siguiente circuito incluyendo la descripción de la entidad y de la arquitectura